### **Greetings from Olaf Vogt**

Director and Head of Application Marketing

**Olaf Vogt** Director and Head of Application Marketing "I would like to thank all participants for joining this first-of-its-kind Nexperia virtual ESD seminar.

The **automotive industry** is driven by the major trends of **electrification**, **autonomous driving and shared 'connected' mobility**.

We also see that ever-increasing data rates, greater calculation power of System-on-Chips and IC miniaturization are making **systems even more sensitive to ESD**.

With our Nexperia ESD Seminar, we want to **support the design community** in protecting applications and products against ESD issues and make systems more reliable.

Additionally, we published an **automotive ESD** application handbook to share our expertise and best practices with you."

Х

# APPLICATION HANDBOOK **AUTOMOTIVE** EDTON **PROTECTION CONCEPTS**, **TESTING & SIMULATION FOR** MODERN INTERFACES Design Engineer's Guide

#### nexperia

#### **Nexperia ESD Seminar Session 1** Fundamentals of ESD Protection

#### Dr. Andreas Hardock

Application Marketing Manager for ESD and EMC <u>andreas.hardock@nexperia.com</u>

#### Lukas Droemer

Product Manager Automotive ESD Protection & Filtering <u>lukas.droemer@nexperia.com</u>

### **ESD Seminar Session 1**

Agenda

- Fundamentals of ESD Protection

- Measurement and Characterization

- Nexperia Lab

- Q&A

### **ESD – Electro Static Discharge**

#### WHAT

A sudden discharge between persons, devices or components

#### HOW

- A charged person touches an integrated circuit (IC)

- A charged IC drops on a grounded metal plate

- A charged machine touches an IC

- An electrostatic field is induced by high voltages

#### PROBLEM

- Causing malfunction (reversible by power-off-on cycle)

- Destruction of electrical components (irreversible): gate oxide, metallisation or PN junctions

### **ESD – Electro Static Discharge**

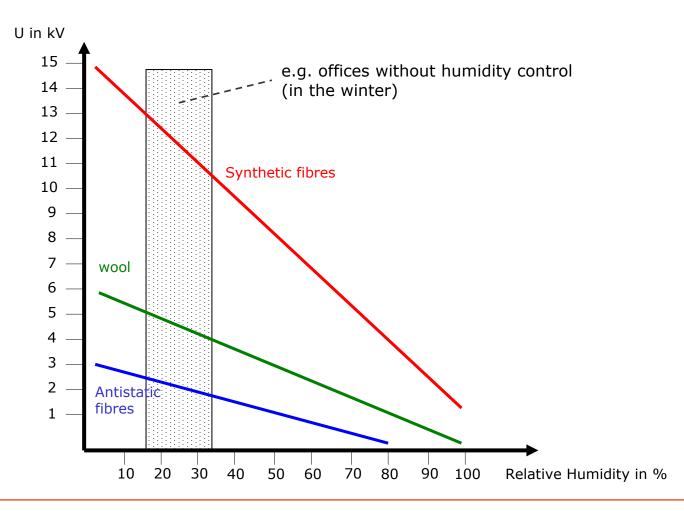

Material / environmental influences affect charge separation

Many materials have potential to cause ESD events

### **ESD – Electro Static Discharge**

#### **Device level**

- ICs can be destroyed (ESD) during placement.

- ESD "on-chip protection" protects against defects during production.

- Qualification by standards (JEDEC)

- Human Body Model (HBM)

- Machine Model (MM)

- Charged Device Model (CDM)

- ESD pulses are given to all IC pins.

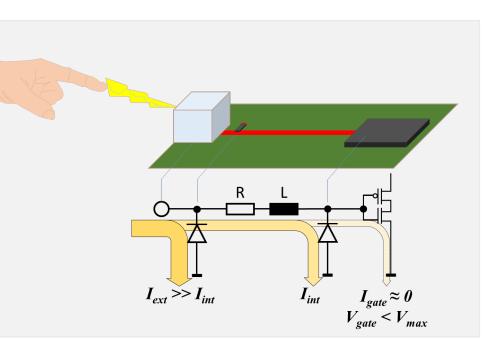

#### System level

- ESD threatens also boards and (complete) devices.

- Special diodes are added on the board to avoid destruction by ESD.

- "System Level" ESD standards

- IEC 61000-4-2

Electrostatic discharge immunity test

- ISO 10605

- ESD pulses are given to certain accessible interfaces.

- Individual components are not tested!

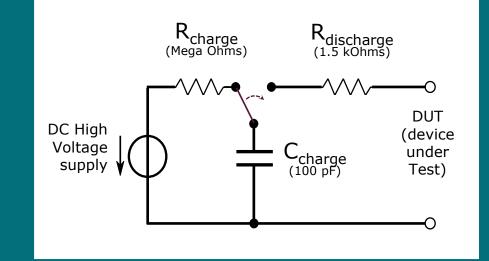

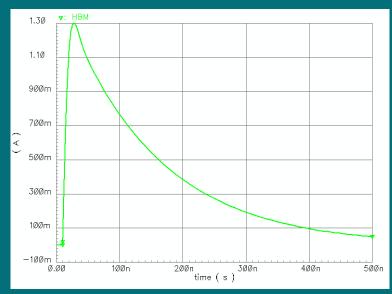

#### **ESD – Device Level Testing: HBM**

Human Body Model

- HBM was developed to simulate the discharge of a human body to a grounded device (IC).

- To replicate an RC network is used:

- R = 1500 ohms

- C = 100 pF

- ANSI / ESDA / JEDEC JS-001-2012 for Semiconductor Components

- **Different** from standard EN 61000-4-2 for devices (system level test)

#### Low current – long duration

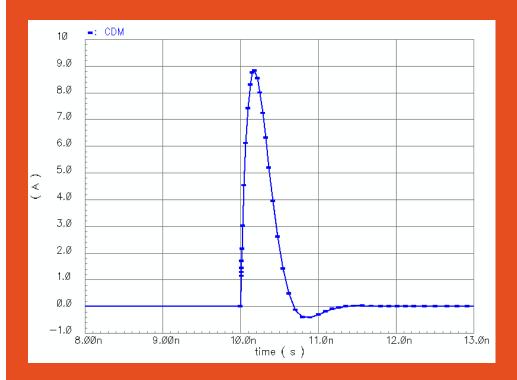

#### **ESD – Device Level Testing: CDM**

Charged Device Model

- CDM emulates the process of charging / discharging that can occur in production environments.

- For example, ICs that are poured from plastic tubes and hit a metallic surface.

- It is conceivable that charges have accumulated on the metal pins of an IC or on the package, ultimately discharging through a single grounded pin.

- The discharge current is limited only by parasitic impedances and capacitance.

# Very high current – very short pulse duration

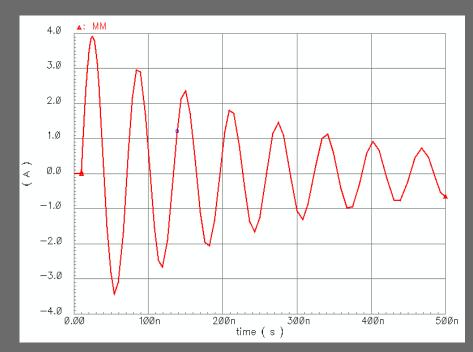

#### **ESD – Device Level Testing: MM**

Machine Model

- MM was developed to model the discharge of a machine to a grounded device (IC).

- Here an RC network is used:

- R = <1 ohm

- C = 200 pF

- Usually replaced by HBM and CDM:

"... JEDEC has strongly recommended discontinuing use of the MM for ESD qualification because of its test variability and non-correlation to real world failure modes"

https://www.esda.org/assets/Uploads/documents/ The-Machine-Model2012.pdf

#### High current – long duration

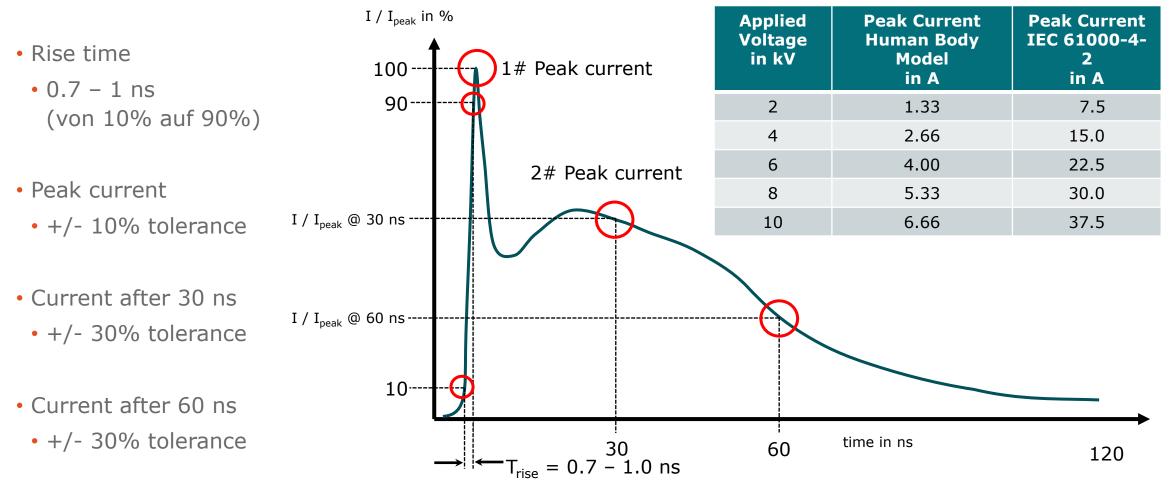

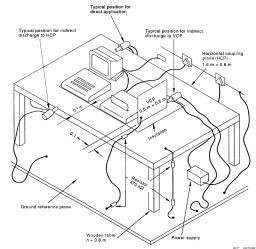

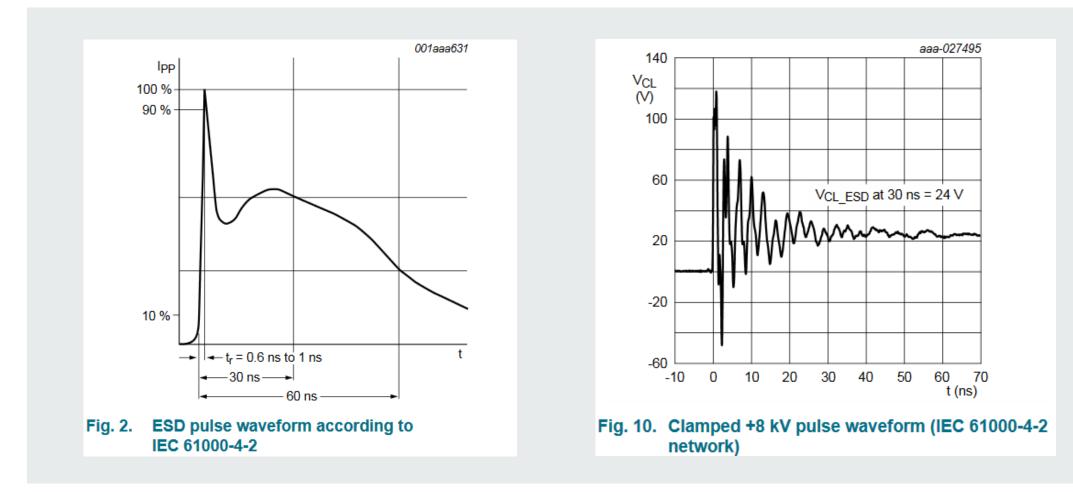

### ESD – System Level Testing: IEC 61000-4-2

Typical waveform of ESD current

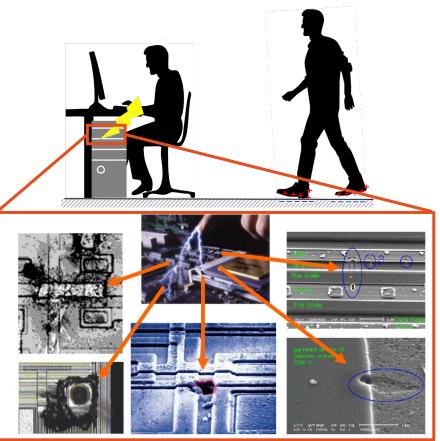

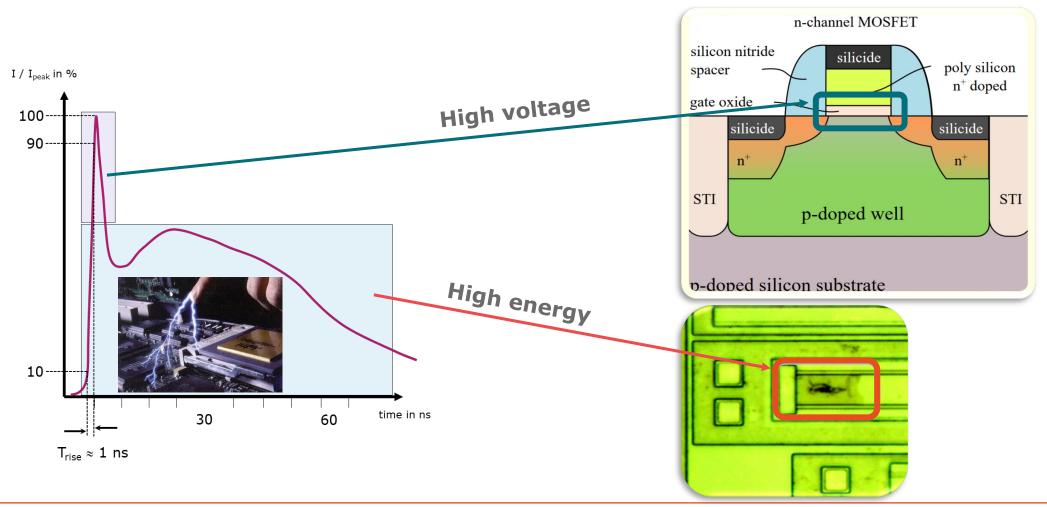

#### **ESD – Defects caused by ESD**

Destruction mechanism

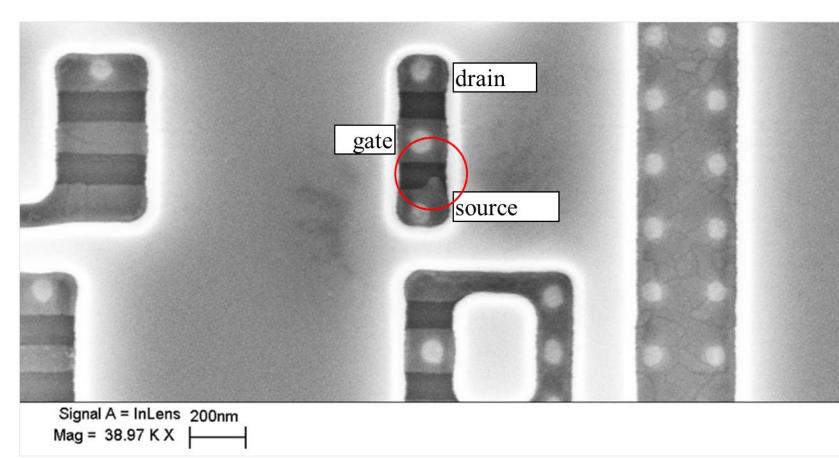

### **ESD – Defects caused by ESD**

#### Destruction mechanism

Bottom (!) view of gate oxide damage after CDM discharge

Deprocessing consisted of grinding Si backside until  $4\mu$ m and removing the remaining Si using a highly selective etch which stops at the SiO2.

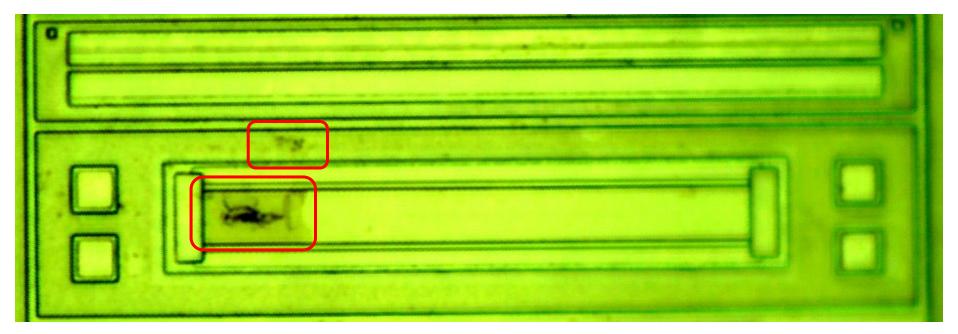

### **ESD – Defects caused by ESD**

Destruction mechanism

Microscope picture of melt damage in large transistor

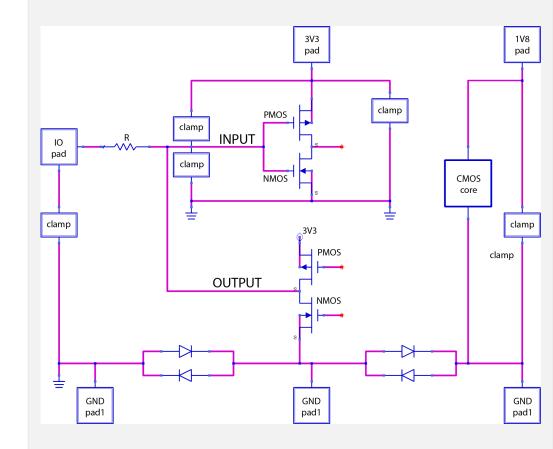

#### **ESD – Protection Strategies inside ICs**

- Integrated circuits (ICs) are usually protected by <u>internal</u> measures against ESD damage.

- This protection is usually only sufficient for manufacturing processes!

- Devices with external interfaces (e.g., CAN, 100Base-T1, USB, HDMI, ...) usually require additional external ESD protection!

### **ESD – Protection Strategies inside ICs**

|     |        | Rev. 3 — 2     | gle P-channel Trenc<br>3 March 2012                            |                    | Product data shee    |

|-----|--------|----------------|----------------------------------------------------------------|--------------------|----------------------|

|     |        | •              |                                                                |                    |                      |

|     | 1      | .1 General des | -                                                              |                    |                      |

|     |        |                | ancement mode Field-Effec<br>SOT883B) Surface-Mounte<br>ology. |                    |                      |

|     | 1      | .2 Features an | d benefits                                                     |                    |                      |

|     |        | Very fast sv   | vitching                                                       | ESD protection u   | p to 2 kV            |

|     |        | Low thresh     | old voltage                                                    | Ultra thin package | e profile of 0.37 mm |

|     |        | Trench MO      | SFET technology                                                |                    |                      |

| Pin | Symbol | Description    | Simplified outline                                             | Graphic symbol     |                      |

| 1   | G      | gate           |                                                                | _                  | D                    |

| 2   | S      | source         | 1                                                              | 3                  |                      |

| 3   | D      | drain          | 2                                                              |                    |                      |

|     |        |                | Transparen<br>top view                                         | t G                |                      |

|     |        |                | DFN1006B                                                       | -3                 |                      |

|     |        |                | (SOT883E                                                       |                    |                      |

|     |        |                |                                                                |                    | S<br>017aaa259       |

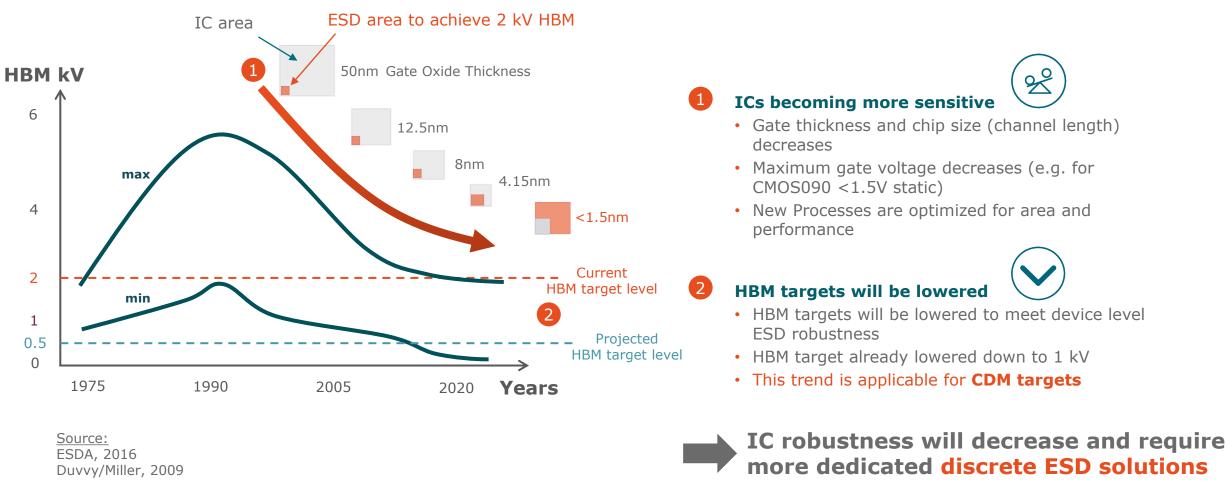

### **ICs become more sensitive**

Increased performance and density lower the SoC ESD robustness

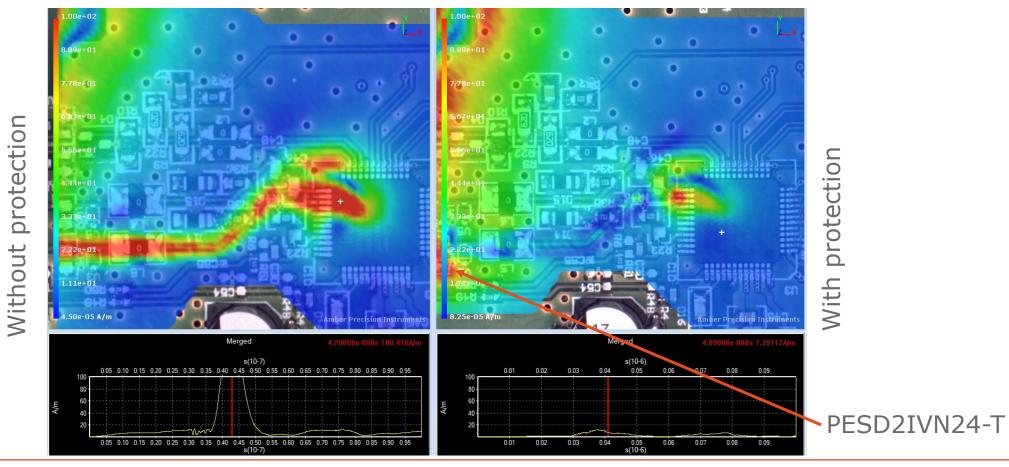

### **Benefits of external ESD protection**

Example CAN bus with PESD2IVN24-T

| IC/Transceiver      | ESD robustness w/o | ESD robustness with PESD2IVN24-T |

|---------------------|--------------------|----------------------------------|

| TLE 9263BQXV33XUMA1 | + 8 kV (HBM)       | + 30 kV                          |

| TLE 9262BQXXUMA1    | + 8 kV (HBM)       | + 30 kV                          |

| MCP25625 E/SS       | + 8 kV (HBM)       | + 30 kV                          |

| LPC11C22FBD48/301   | + 8 kV (HBM)       | + 30 kV                          |

| SN65HVD232QDRQ1     | + 11 kV (HBM)      | + 30 kV                          |

| TLE7250GXUMA1       | + 10 kV (HBM)      | + 30 kV                          |

| TJA1042T/3,118      | + 12 kV (HBM)      | + 30 kV                          |

| TJA1044T            | + 10 kV (HBM)      | + 30 kV                          |

| ÷                   | ÷                  | +30 kV                           |

External ESD Protection can handle much more current and can be chosen application specific.

## **ESD Seminar Session 1**

Agenda

- Fundamentals of ESD Protection

- Measurement and Characterization

- Nexperia Lab

- Q&A

#### **Measurement and Characterization**

Agenda

- Selection Criterion

- ESD Tolerance Test

- Clamping Voltage

- Peak Pulse Current

- Dynamic Resistance using TLP

DEN1006B

Package (shape/size/footprint)

Side-wettable flanks for AOI

Number of signal lines

Electrical performance

- Reverse stand-off voltage  $V_{RWM}$

- ESD robustness level  $V_{ESD}$

- Clamping voltage V<sub>clamp</sub>

- Dynamic resistance R<sub>dyn</sub>

- Topology: uni- / bi-directional, rail to rail, ...

- Device capacitance C<sub>diode</sub> and other parasitics

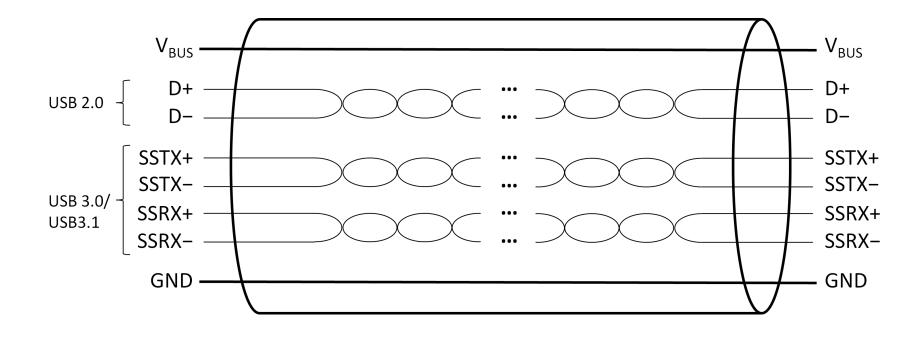

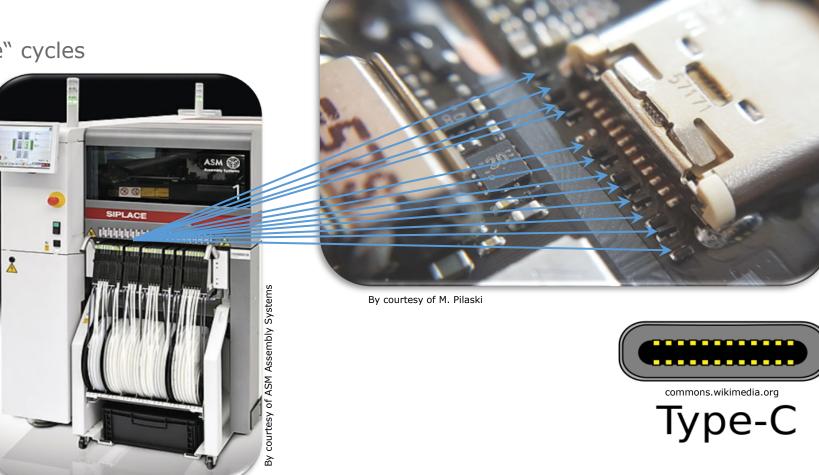

Selection Criteria: Number of signal lines

• Single signal line vs. multiple similar lines, e.g. USB 3.0

Selection Criteria: Number of signal lines / Package

- Number of "pick and place" cycles

- Stock keeping

- Bulk purchase

- Second source

- Easy routing (layout)

$\underline{\mathbf{R}}$ everse  $\underline{\mathbf{W}}$ orking  $\underline{\mathbf{M}}$ aximum Voltage  $\mathbf{V}_{\mathbf{RWM}}$

#### • PESD2IVN24-T

| $V_{RWM}$ reverse standoff voltage $T_{amb} = 25 ^{\circ}C$ Image: Constraint of the standoff voltage $T_{amb} = 25 ^{\circ}C$ Image: Constraint of the standoff voltage $I_R = 10  \text{mA}; T_{amb} = 25 ^{\circ}C$ Image: Constraint of the standoff voltage $I_R = 10  \text{mA}; T_{amb} = 25 ^{\circ}C$ Image: Constraint of the standoff voltage $I_R = 10  \text{mA}; T_{amb} = 25 ^{\circ}C$ Image: Constraint of the standoff voltage $I_R = 10  \text{mA}; T_{amb} = 25 ^{\circ}C$ Image: Constraint of the standoff voltage $I_R = 10  \text{mA}; T_{amb} = 25 ^{\circ}C$ Image: Constraint of the standoff voltage $I_R = 10  \text{mA}; T_{amb} = 25 ^{\circ}C$ Image: Constraint of the standoff voltage $I_R = 10  \text{mA}; T_{amb} = 25 ^{\circ}C$ Image: Constraint of the standoff voltage $I_R = 10  \text{mA}; T_{amb} = 25 ^{\circ}C$ Image: Constraint of the standoff voltage $I_R = 10  \text{mA}; T_{amb} = 25 ^{\circ}C$ Image: Constraint of the standoff voltage $I_R = 10  \text{mA}; T_{amb} = 25 ^{\circ}C$ Image: Constraint of the standoff voltage $I_R = 10  \text{mA}; T_{amb} = 25 ^{\circ}C$ Image: Constraint of the standoff voltage $I_R = 10  \text{mA}; T_{amb} = 25 ^{\circ}C$ Image: Constraint of the standoff voltage $I_R = 10  \text{mA}; T_{amb} = 25 ^{\circ}C$ Image: Constraint of the standoff voltage $I_R = 10  \text{mA}; T_{amb} = 25 ^{\circ}C$ Image: Constraint of the standoff voltage $I_R = 10  \text{mA}; T_{amb} = 25 ^{\circ}C$ Image: Constraint of the standoff voltage $I_R = 10  \text{mA}$ |                  |                            |                                                   |     |      |      |      |      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------------------|---------------------------------------------------|-----|------|------|------|------|

| voltage         voltage         Image                                                                                                                                                                                                                                                                                            | Symbol           | Parameter                  | Conditions                                        |     | Min  | Тур  | Max  | Unit |

| I <sub>RM</sub> reverse leakage V <sub>RWM</sub> = 24 V; T <sub>amb</sub> = 25 °C [1] - 1 50 nA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | V <sub>RWM</sub> |                            | T <sub>amb</sub> = 25 °C                          |     | -    | -    | 24   | V    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | V <sub>BR</sub>  | breakdown voltage          | I <sub>R</sub> = 10 mA; T <sub>amb</sub> = 25 °C  | [1] | 25.5 | 30.5 | 35.5 | V    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | I <sub>RM</sub>  | reverse leakage<br>current | V <sub>RWM</sub> = 24 V; T <sub>amb</sub> = 25 °C | [1] | -    | 1    | 50   | nA   |

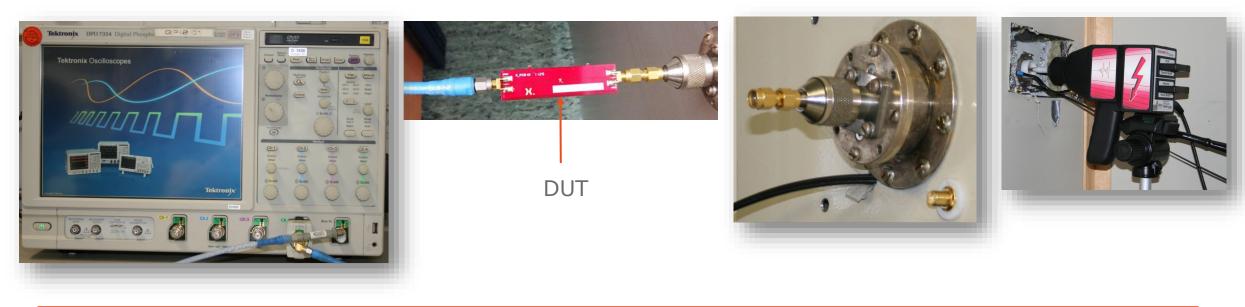

#### ESD Tolerance Test – Measurement Equipment

ESD Simulator (Gun): ESD 30000, Schlöder GmbH

Semiconductor Parameter Analyzer: HP4145B, Agilent Technologies

Digital Multi Meter:

Agilent 34401A, Agilent Technologies

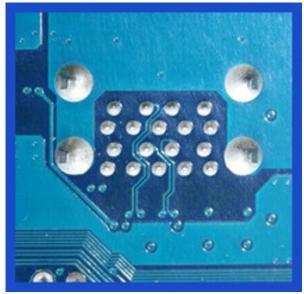

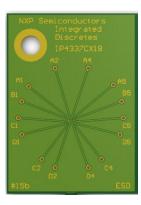

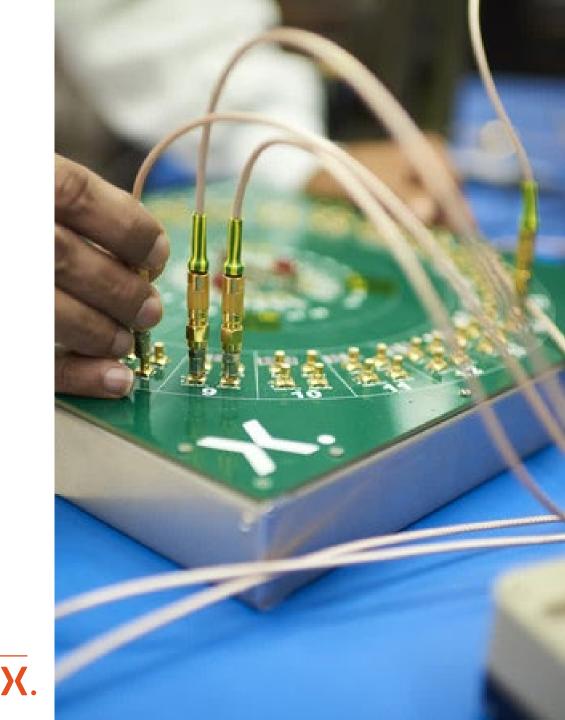

#### Typical ESD test PCB:

4 Layer PCB stack up with 1.5mm total thickness approx.

15mm track length from pad for ESD Simulator to DUT pad

280um track width

200um spacing

35um Cu thickness

Top layer Cu filled

2nd layer GND plane

GND Via in DUT footprint: 150µm Cu filled

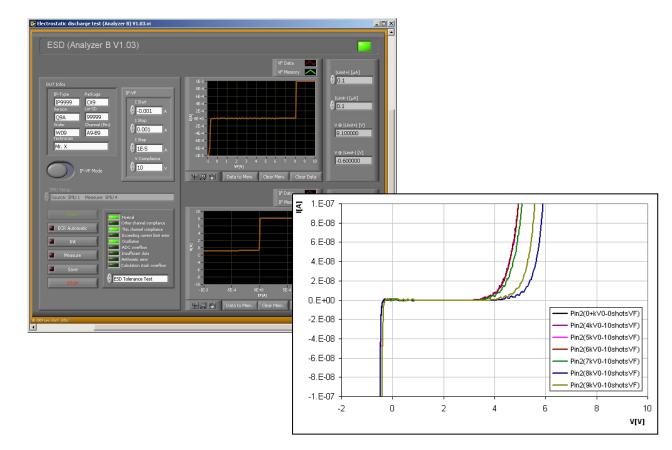

### **ESD Tolerance Test – Failure testing**

After each test level, device characteristics will be checked by comparing initial curve progression vs. actual curve progression

#### Detection of "fail" DUT by:

Modified break down voltage Higher leakage current Changed series resistor Abnormal curve progression

#### For characterization purpose

Curve progression V = f(I)Curve progression I = f(V)

are analyzed and will be stored as MS Excel file

#### **ESD Robustness**

ESD Robustness / ESD Rating / ESD Tolerance

#### • PESD2IVN24-T:

| ESD maxir        | mum ratings                        |                                                               |                             |   |    |             |

|------------------|------------------------------------|---------------------------------------------------------------|-----------------------------|---|----|-------------|

| V <sub>ESD</sub> | electrostatic discharge<br>voltage | IEC 61000-4-2; contact discharge                              | [2] [3]                     | - | 30 | kV          |

|                  |                                    | ISO 10605; contact discharge;<br>C = 330 pF, R = 330 $\Omega$ | [2] [3]                     | - | 30 | k∨          |

|                  |                                    | ISO 10605; contact discharge;<br>C = 150 pF, R = 330 Ω        | [2] [3]                     | - | 30 | k∨          |

|                  |                                    |                                                               | d from pin 1<br>ressed with |   |    | ESD pulses. |

- ESD Robustness of the device alone

- $\rightarrow$  This value does not allow to draw conclusion about system level ESD robustness

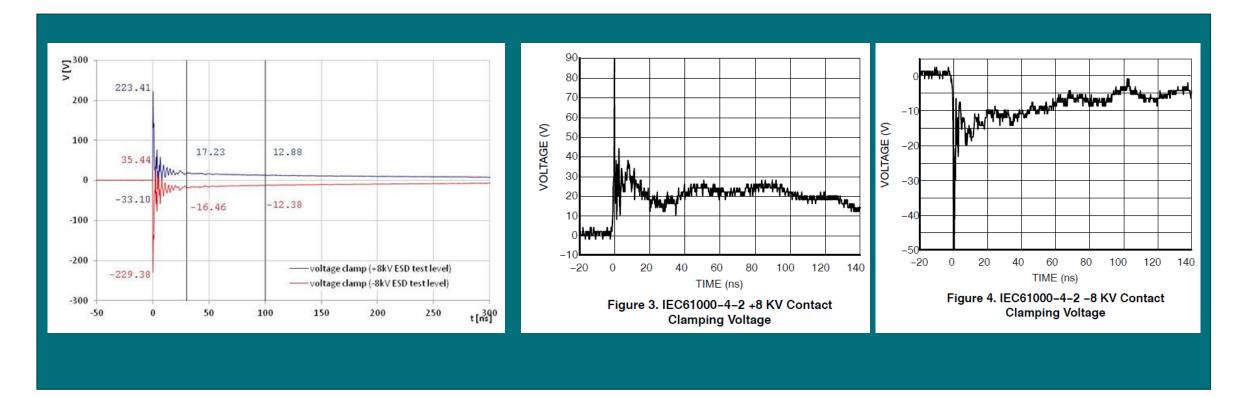

### **ESD – Clamping Voltage**

Clamping voltage V<sub>clamp</sub> e.g. for 8 kV ESD pulse – PESD2IVN24-T

### Clamping voltage according to IEC61000-4-2

The usage of a high sample rate at the oscilloscope is very important Measurement with low sample rate can be seen in some datasheets to tune results.

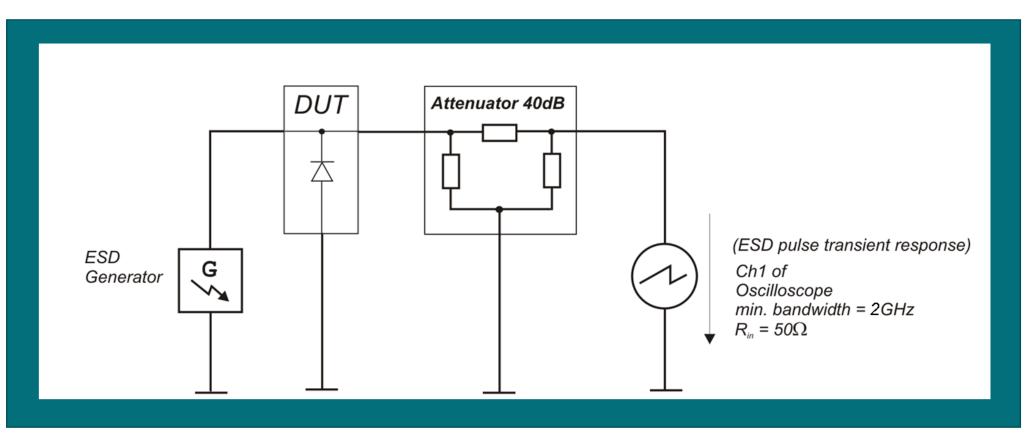

#### Vcl measurement setup (IEC61000-4-2 wave form)

Connection to DUT and Scope

SMA connectorsDUT on PCB with 50 Ohm matched impedance lines40 dB attenuator3.5 GHz Scope (Tektronix DPO 7354)

### **Clamping voltage: Too low sampling**

Measurement of competitor ESD protection devices in Nexperia lab compared to datasheet values

Sampling with a high frequency, at least 2GHz

Sampling with a low frequency

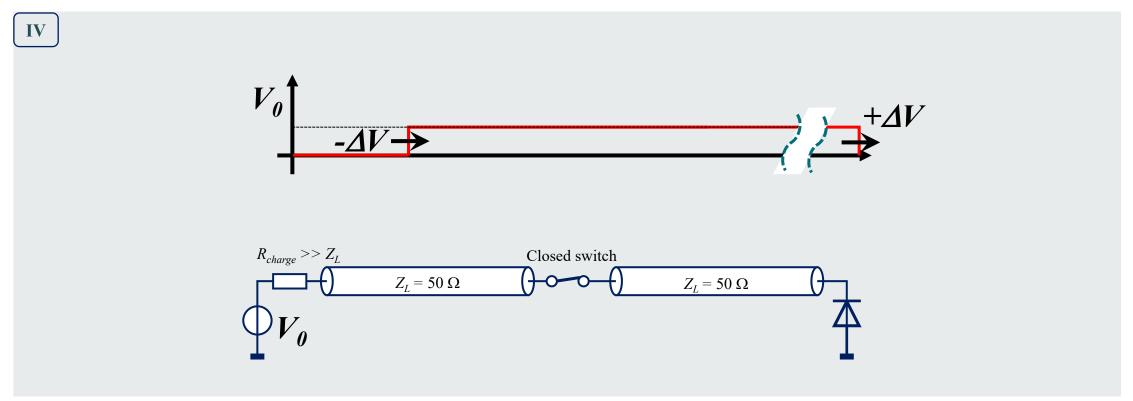

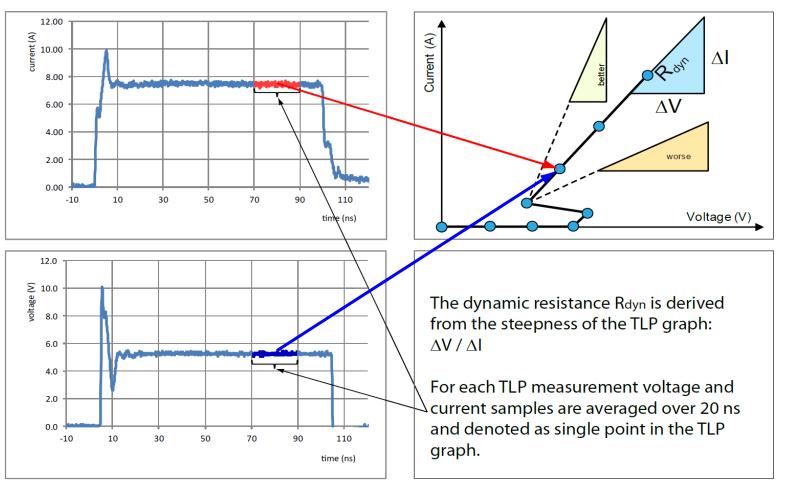

Transmission Line Pulse

• High impedance charge resistor reflects voltage change back into coaxial line

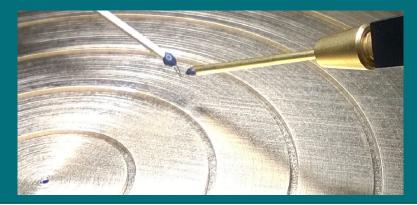

#### **TLP Test** – Set up for component testing

#### **HPPI TLP generator** Generator

#### Switch-box

**Needle probes** DUT is put backside down on an ceramic insulator tile. The 2 needle pairs are contacted directly (signal pad; ground pad)

#### **Microscope for** needle testing

With micro manipulators

Two needle pairs for powerless sense

Transmission Line Pulse

- Typical pulse width 100 ns

- VF-TLP (very fast) ~3 ns

- Number of pulses with increased voltage

- Every pulse leads to an measurement point in IV curve

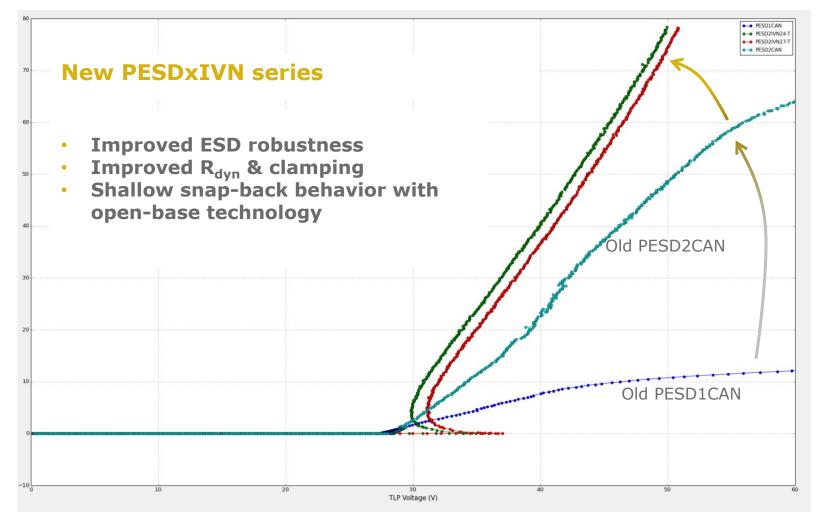

#### **TLP Graphs Comparison**

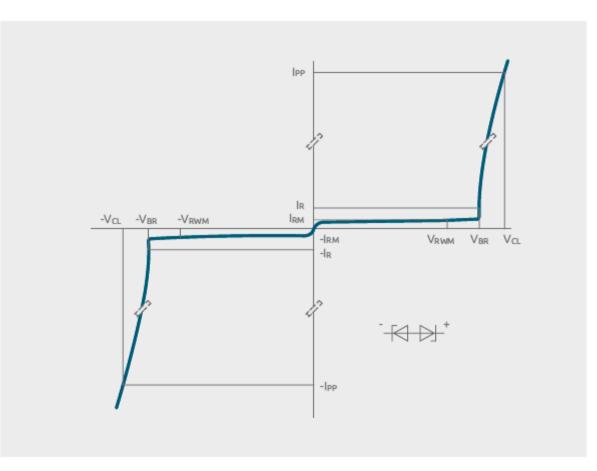

#### **Characteristics of ESD Protections**

Classical Zener Characteristic

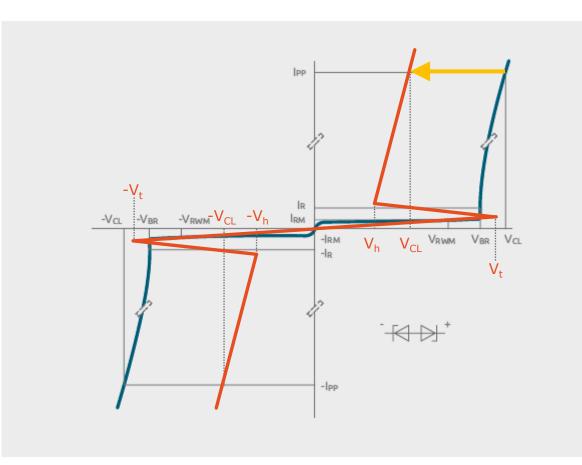

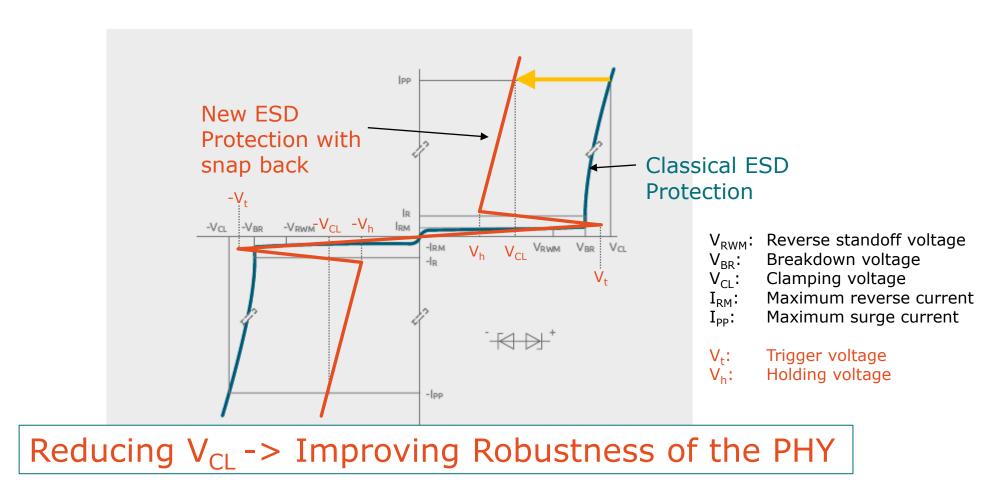

#### **Characteristics of new ESD Protections**

Snap Back

Reverse standoff voltage V<sub>RWM</sub>: V<sub>BR</sub>: Breakdown voltage V<sub>CL</sub>: Clamping voltage Maximum reverse current I<sub>RM</sub>: I<sub>PP</sub>: Maximum surge current

Trigger voltage V<sub>h</sub>: Holding voltage

$V_{t}$ :

### **Characteristics of new ESD Protections**

Snap Back

# ESD Seminar Session 1

Agenda

- Fundamentals of ESD Protection

- Measurement and Characterization

- Nexperia Lab

- Q&A

### Nexperia Lab

Only on customer request

With our dedicated team we offer a broad variety of design support. This includes:

- Design review and error tracking from application to device level

- Analysis tools

- Device characterization with TLP measurements

- PCB screening with EMI scanner

- SEED modelation and simulation

- S-Parameters, (RF)-SPICE models and others

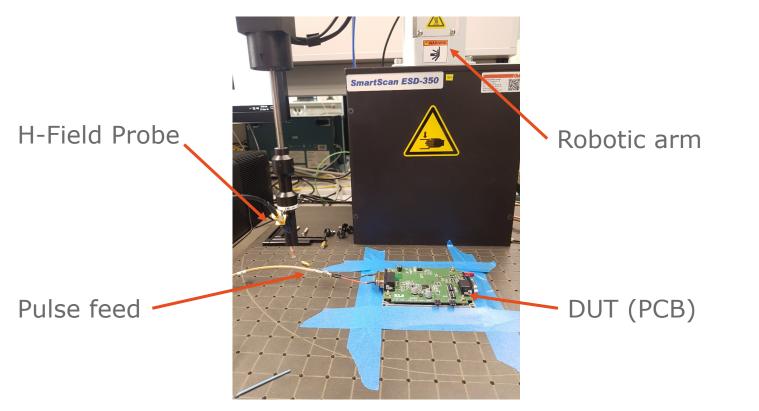

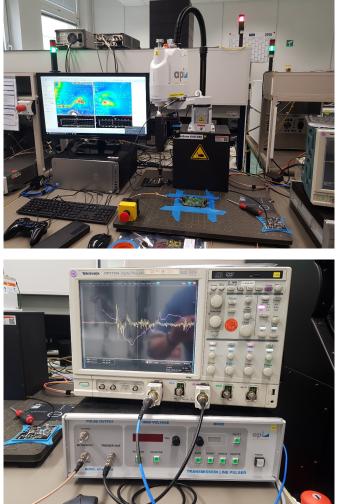

#### **EMI - Scanner**

To measure how the ESD pulse distribute across the PCB

Pulse generator

#### **EMI - Scanner**

To measure how the ESD pulse distribute across the PCB

CAN Transceiver reference board

41

#### **Service & Support**

Find out more about Nexperia and our products & services

| <image/>                                                                                                                                                                                                      | Sector Guide         Descuration Center         Link Selection Guide                                                                                                                     | ESSE<br>APPLICATION<br>HANDBOOK<br>AUTOMOTIVE<br>EDITION<br>PROTECTION CONCEPTS,<br>TESTIMA SIMULATION FOR<br>MODERN INTERFACES<br>Design Engineer's Cuide<br>ne perita              | <b>Lab support</b>                                                                                                                                                                                                              |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Search Function</li> <li>Cross Reference</li> <li>Parametric Search</li> <li>Package Search</li> <li>Product Overview [Path to Datasheets, Product<br/>Brochures, Application Examples,] </li> </ul> | <ul> <li>Overview on all our<br/>Discrete, Logic and<br/>MOSFET devices</li> <li>Diodes &amp; Transistors</li> <li>Protection &amp; Filtering</li> <li>MOSFETs</li> <li>Logic</li> </ul> | <ul> <li>Automotive interfaces and applications</li> <li>Testing standards</li> <li>Simulation methods</li> <li>English &amp; Chinese version</li> <li>PDF &amp; Hardcopy</li> </ul> | <ul> <li>Dedicated engineering<br/>team to support customer<br/>requests</li> <li>Solution investigation with<br/>various analysis tools<br/>especially</li> <li>TLP, EMI scan, SEED</li> <li>Contact us for details</li> </ul> |

ESD for Electronic Design Engineers Seminar

# nexperia

EFFICIENCY WINS.

#### EFFICIENCY WINS.