外形图

| 封装版本 | 封装名称 | 封装说明 | 参考 | 发行日期 |

|---|---|---|---|---|

| SOT765-1 | VSSOP8 | plastic, very thin shrink small outline package; 8 leads; 0.5 mm pitch; 2 mm x 2.3 mm x 1 mm body | MO-187 (JEDEC) | 2016-05-31 |

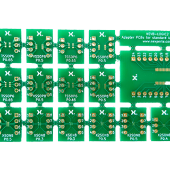

Boards

| Part number | Description | Type | Quick links | Shop link |

|---|---|---|---|---|

|

描述 NEVB-LOGIC02 is a dual in-line logic footprint adapter board, designed to simplify the evaluation of Nexperia logic devices by offering several package footprints.

|

类型 Evaluation board

|

Quick links

|

Shop link

|

相关文档

| 文件名称 | 标题 | 类型 | 日期 |

|---|---|---|---|

| AN90063 | Questions about package outline drawings | Application note | 2025-10-22 |

| Nexperia_document_guide_MiniLogic_PicoGate_201901 | PicoGate leaded logic portfolio guide | Brochure | 2019-01-07 |

| SOT765-1 | 3D model for products with SOT765-1 package | Design support | 2020-01-22 |

| Nexperia_package_poster | Nexperia package poster | Leaflet | 2020-05-15 |

| VSSOP8_SOT765-1_mk | plastic, very thin shrink small outline package; 8 leads; 0.5 mm pitch; 2 mm x 2.3 mm x 1 mm body | Marcom graphics | 2017-01-28 |

| SOT765-1 | plastic, very thin shrink small outline package; 8 leads; 0.5 mm pitch; 2 mm x 2.3 mm x 1 mm body | Package information | 2022-06-03 |

| SOT765-1_125 | VSSOP8; Reel pack for SMD, 7''; Q3/T4 product orientation | Packing information | 2025-10-24 |

采用此封装的产品

Analog & Logic ICs

| 型号 | 描述 | 快速访问 |

|---|---|---|

| 74LVC2G66DC | Bilateral switch | |

| 74LVC3G07DC | Triple buffer with open-drain output | |

| 74LVC2G38DC | Dual 2-input NAND gate; open drain | |

| 74LVC2G67DC-Q100 | Bilateral switch | |

| 74LVC2G53DC | 2-channel analog multiplexer/demultiplexer | |

| 74AUP2G157DC | Low-power 2-input multiplexer | |

| 74LVCV2G66DC | Overvoltage tolerant bilateral switch | |

| 74CBTLV3306DC | 2-bit bus switch | |

| 74AUP2G38DC | Low-power dual 2-input NAND gate; open drain | |

| 74AVC2T45DC | Dual-bit, dual-supply voltage level translator/transceiver; 3-state | |

| 74AVCH2T45DC | Dual-bit, dual-supply voltage level translator/transceiver; 3-state | |

| 74LVC2G125DC | Dual bus buffer/line driver; 3-state | |

| 74LVC3G34DC | Triple buffer | |

| NXB0102DC | Dual supply translating transceiver; auto direction sensing; 3-state | |

| 74LVC2T45DC | Dual supply translating transceiver; 3-state | |

| 74LVC2G240DC | Dual inverting buffer/line driver; 3-state | |

| 74AUP2G240DC | Low-power dual inverting buffer/line driver; 3-state | |

| 74AUP2G125DC | Low-power dual buffer/line driver; 3-state | |

| 74AUP2G241DC | Low-power dual buffer/line driver; 3-state | |

| 74AUP2G126DC | Low-power dual buffer/line driver; 3-state | |

| 74AUP3G07DC | Low-power triple buffer with open-drain output | |

| 74AUP3G04DC | Low-power triple inverter | |

| 74AUP3G16DC | Low-power triple buffer | |

| 74AUP3G34DC | Low-power triple buffer | |

| 74LVC3G17DC | Triple non-inverting Schmitt trigger with 5 V tolerant input | |

| 74LVC3G14DC | Triple inverting Schmitt trigger with 5 V tolerant input | |

| 74AHC2G126DC | Dual buffer/line driver; 3-state | |

| 74AHC2G241DC | Dual buffer/line driver; 3-state | |

| 74AHC3GU04DC | Triple unbuffered inverter | |

| 74AHC3G04DC | Inverter | |

| 74AHCT2G125DC | Dual buffer/line driver; 3-state | |

| 74AHCT2G241DC | Dual buffer/line driver; 3-state | |

| 74AHCT2G126DC | Dual buffer/line driver; 3-state | |

| 74AHCT3G04DC | Inverter | |

| 74AXP2T45DC | 2-bit dual supply translating transceiver; 3-state | |

| XC7WH126DC | Dual buffer/line driver; 3-state | |

| NXU0202DC | 2-bit dual-supply buffer/level translator with Schmitt-trigger inputs; 3-state | |

| NXU0102DC | 2-bit dual-supply buffer/level translator with Schmitt-trigger; 3-state | |

| 74HC2G125DC | Dual buffer/line driver; 3-state | |

| 74HC3G06DC | Triple inverter with open-drain outputs | |

| 74HC3G04DC | Triple inverter | |

| 74HC3G07DC | Triple buffer with open-drain outputs | |

| 74HC3GU04DC | Triple unbuffered inverter | |

| 74HC3G34DC | Triple buffer gate | |

| 74HCT2G125DC | Dual buffer/line driver; 3-state | |

| 74HCT3G06DC | Triple inverter with open-drain outputs | |

| 74HCT3G04DC | Triple inverter | |

| 74HCT3G07DC | Triple buffer with open-drain outputs | |

| 74HCT3G34DC | Triple buffer gate | |

| 74HCT3G14DC | Triple inverting Schmitt trigger | |

| 74HC3G14DC | Triple inverting Schmitt trigger | |

| 74AUP2G132DC | Low-power dual 2-input NAND Schmitt trigger | |

| 74AUP3G14DC | Low-power triple Schmitt trigger inverter | |

| 74AUP3G17DC | Low-power triple Schmitt trigger | |

| 74AVC9112DC | 1-to-4 fan-out buffer | |

| 74AHC3G14DC | Triple inverting Schmitt trigger | |

| 74AHCT3G14DC | Triple inverting Schmitt trigger | |

| XC7WH14DC | Triple inverting Schmitt trigger | |

| 74AHC2G125DC | Dual buffer/line driver; 3-state | |

| 74LVC3G06DC | Triple inverter with open-drain output | |

| 74LVC3G04DC | Triple inverter | |

| 74LVC2G241DC | Dual buffer/line driver; 3-state | |

| 74LVC2G126DC | Dual bus buffer/line driver; 3-state | |

| 74LVCH2T45DC | Dual supply translating transceiver; 3-state | |

| 74LVC3GU04DC | Triple unbuffered inverter | |

| LSF0102DC | 2-bit bidirectional multi-voltage level translator; open-drain; push-pull | |

| NXS0102DC | Dual supply translating transceiver; open drain; auto direction sensing | |

| LSF0202DC | 2-bit bidirectional multi-voltage level translator; open-drain; push-pull | |

| 74AUP1G885DC | Low-power dual function gate | |

| 74HC2G08DC | Dual 2-input AND gate | |

| 74AUP2G86DC | Low-power dual 2-input EXCLUSIVE-OR gate | |

| 74AHCT2G08DC | Dual 2-input AND gate | |

| 74AUP2G08DC | Low-power dual 2-input AND gate | |

| 74HC2G32DC | Dual 2-input OR gate | |

| 74HCT2G08DC | Dual 2-input AND gate | |

| 74AUP3G3404DC | Low-power dual buffer and single inverter | |

| 74HC2G02DC | Dual 2-input NOR gate | |

| 74AUP2G00DC | Low-power dual 2-input NAND gate | |

| 74AUP3G0434DC | Low-power dual inverter and single buffer | |

| 74LVC2G86DC | Dual 2-input EXCLUSIVE-OR gate | |

| 74LVC2G02DC | Dual 2-input NOR gate | |

| 74AHC2G32DC | Dual 2-input OR gate | |

| 74AUP2G02DC | Low-power dual 2-input NOR gate | |

| 74AHCT2G32DC | Dual 2-input OR gate | |

| 74HCT2G02DC | Dual 2-input NOR gate | |

| 74LVC2G08DC | Dual 2-input AND gate | |

| 74AUP2G32DC | Low-power dual 2-input OR gate | |

| 74HCT2G32DC | Dual 2-input OR gate | |

| 74AHC2G00DC | Dual 2-input NAND gate | |

| 74LVC2G74DC | Single D-type flip-flop with set and reset; positive edge trigger | |

| 74LVC2G00DC | Dual 2-input NAND gate | |

| 74AUP1G74DC | Low-power D-type flip-flop with set and reset; positive-edge trigger | |

| 74LVC1G74DC | Single D-type flip-flop with set and reset; positive edge trigger | |

| 74AHC2G126DC-Q100 | Dual buffer/line driver; 3-state | |

| 74AHC2G00DC-Q100 | Dual 2-input NAND gate | |

| 74AHC3GU04DC-Q100 | Triple unbuffered inverter | |

| 74AHC3G14DC-Q100 | Triple inverting Schmitt trigger | |

| 74AHC3G04DC-Q100 | Inverter | |

| 74AHCT2G126DC-Q100 | Dual buffer/line driver; 3-state | |

| 74AHCT2G32DC-Q100 | Dual 2-input OR gate | |

| 74AHCT2G125DC-Q100 | Dual buffer/line driver; 3-state | |

| 74AHCT2G00DC-Q100 | Dual 2-input NAND gate | |

| 74AHCT3G04DC-Q100 | Inverter | |

| 74AHCT2G08DC-Q100 | Dual 2-input AND gate | |

| 74HC2G02DC-Q100 | Dual 2-input NOR gate | |

| 74HC3G04DC-Q100 | Triple inverter | |

| 74HC3G34DC-Q100 | Triple buffer gate | |

| 74HCT3G07DC-Q100 | Triple buffer with open-drain outputs | |

| 74AVCH2T45DC-Q100 | Dual-bit, dual-supply voltage level translator/transceiver; 3-state | |

| 74HC3G14DC-Q100 | Triple inverting Schmitt trigger | |

| 74HC2G08DC-Q100 | Dual 2-input AND gate | |

| 74AUP2G08DC-Q100 | Low-power dual 2-input AND gate | |

| 74LVC1G123DC-Q100 | Single retriggerable monostable multivibrator; Schmitt trigger inputs | |

| 74HCT2G08DC-Q100 | Dual 2-input AND gate | |

| 74HCT2G66DC | Dual single-pole single-throw analog switch | |

| 74HC2G66DC | Dual single-pole single-throw analog switch | |

| 74LVC1G53DC | 2-channel analog multiplexer/demultiplexer | |

| 74AHC2G08DC | Dual 2-input AND gate | |

| 74HC2G86DC | Dual 2-input EXCLUSIVE-OR gate | |

| 74AHCT2G00DC | Dual 2-input NAND gate | |

| 74LVC2G32DC | Dual 2-input OR gate | |

| 74HC2G00DC | Dual 2-input NAND gate | |

| 74HCT2G00DC | Dual 2-input NAND gate | |

| 74HCT2G86DC | Dual 2-input EXCLUSIVE-OR gate | |

| 74AUP2G80DC | Low-power dual D-type flip-flop; positive-edge trigger | |

| 74AUP2G79DC | Low-power dual D-type flip-flop; positive-edge trigger | |

| 74LVC1G123DC | Single retriggerable monostable multivibrator; Schmitt trigger inputs | |

| 74HC3GU04DC-Q100 | Triple unbuffered inverter | |

| 74AHC2G08DC-Q100 | Dual 2-input AND gate | |

| 74AHC2G241DC-Q100 | Dual buffer/line driver; 3-state | |

| 74AHC2G125DC-Q100 | Dual buffer/line driver; 3-state | |

| 74AHC2G32DC-Q100 | Dual 2-input OR gate | |

| 74AHCT2G241DC-Q100 | Dual buffer/line driver; 3-state | |

| 74HC2G125DC-Q100 | Dual buffer/line driver; 3-state | |

| 74AHCT3G14DC-Q100 | Triple inverting Schmitt trigger | |

| 74AUP1G74DC-Q100 | Low-power D-type flip-flop with set and reset; positive-edge trigger | |

| 74AUP2G00DC-Q100 | Low-power dual 2-input NAND gate | |

| 74AUP2G80DC-Q100 | Low-power dual D-type flip-flop; positive-edge trigger | |

| 74HC2G00DC-Q100 | Dual 2-input NAND gate | |

| 74HCT2G32DC-Q100 | Dual 2-input OR gate | |

| 74AUP2G79DC-Q100 | Low-power dual D-type flip-flop; positive-edge trigger | |

| 74AVC2T45DC-Q100 | Dual-bit, dual-supply voltage level translator/transceiver; 3-state | |

| 74AUP2G125DC-Q100 | Low-power dual buffer/line driver; 3-state | |

| 74HCT3G04DC-Q100 | Triple inverter | |

| 74HC2G66DC-Q100 | Dual single-pole single-throw analog switch | |

| 74HC2G86DC-Q100 | Dual 2-input EXCLUSIVE-OR gate | |

| 74HC2G32DC-Q100 | Dual 2-input OR gate | |

| 74HC3G07DC-Q100 | Triple buffer with open-drain outputs | |

| 74HCT3G34DC-Q100 | Triple buffer gate | |

| 74HCT2G00DC-Q100 | Dual 2-input NAND gate | |

| 74HCT2G02DC-Q100 | Dual 2-input NOR gate | |

| 74LVC2G125DC-Q100 | Dual bus buffer/line driver; 3-state | |

| 74HCT3G14DC-Q100 | Triple inverting Schmitt trigger | |

| 74HCT2G86DC-Q100 | Dual 2-input EXCLUSIVE-OR gate | |

| 74LVC2G00DC-Q100 | Dual 2-input NAND gate | |

| 74LVC2G32DC-Q100 | Dual 2-input OR gate | |

| 74LVC3G17DC-Q100 | Triple non-inverting Schmitt trigger with 5 V tolerant input | |

| 74LVC3GU04DC-Q100 | Triple unbuffered inverter | |

| 74LVC1G53DC-Q100 | 2-channel analog multiplexer/demultiplexer | |

| 74HCT2G125DC-Q100 | Dual buffer/line driver; 3-state | |

| 74HCT2G66DC-Q100 | Dual single-pole single-throw analog switch | |

| 74LVC2G74DC-Q100 | Single D-type flip-flop with set and reset; positive edge trigger | |

| 74LVC3G34DC-Q100 | Triple buffer | |

| 74LVC2G08DC-Q100 | Dual 2-input AND gate | |

| 74LVC2T45DC-Q100 | Dual supply translating transceiver; 3-state | |

| 74LVC1G74DC-Q100 | Single D-type flip-flop with set and reset; positive edge trigger | |

| 74LVC2G66DC-Q100 | Bilateral switch | |

| 74LVC2G241DC-Q100 | Dual buffer/line driver; 3-state | |

| 74LVCH2T45DC-Q100 | Dual supply translating transceiver; 3-state | |

| 74LVC2G126DC-Q100 | Bus buffer/line driver; 3-state | |

| 74LVC2G02DC-Q100 | Dual 2-input NOR gate | |

| 74LVC2G240DC-Q100 | Dual inverting buffer/line driver; 3-state | |

| LSF0102DC-Q100 | 2-bit bidirectional multi-voltage level translator; open-drain; push-pull | |

| 74LVC2G86DC-Q100 | Dual 2-input EXCLUSIVE-OR gate | |

| 74LVC3G07DC-Q100 | Triple buffer with open-drain output | |

| 74LVC3G04DC-Q100 | Triple inverter | |

| NXS0102DC-Q100 | Dual supply translating transceiver; open drain; auto direction sensing | |

| NXU0102DC-Q100 | 2-bit dual-supply buffer/level translator with Schmitt-trigger; 3-state | |

| NXU0202DC-Q100 | 2-bit dual-supply buffer/level translator with Schmitt-trigger; 3-state | |

| NXB0102DC-Q100 | Dual supply translating transceiver; auto direction sensing; 3-state | |

| 74LVC2G67DC | Bilateral switch | |

| NCA9306DC-Q100 | 2-bit bidirectional multi-voltage level translator; open-drain; push-pull | |

| NCA9306DC | 2-bit bidirectional multi-voltage level translator; open-drain; push-pull |

Automotive qualified products (AEC-Q100/Q101)

| 型号 | 描述 | 快速访问 |

|---|---|---|

| 74LVC2G67DC-Q100 | Bilateral switch | |

| 74AHC2G126DC-Q100 | Dual buffer/line driver; 3-state | |

| 74AHC2G00DC-Q100 | Dual 2-input NAND gate | |

| 74AHC3GU04DC-Q100 | Triple unbuffered inverter | |

| 74AHC3G14DC-Q100 | Triple inverting Schmitt trigger | |

| 74AHC3G04DC-Q100 | Inverter | |

| 74AHCT2G126DC-Q100 | Dual buffer/line driver; 3-state | |

| 74AHCT2G32DC-Q100 | Dual 2-input OR gate | |

| 74AHCT2G125DC-Q100 | Dual buffer/line driver; 3-state | |

| 74AHCT2G00DC-Q100 | Dual 2-input NAND gate | |

| 74AHCT3G04DC-Q100 | Inverter | |

| 74AHCT2G08DC-Q100 | Dual 2-input AND gate | |

| 74HC2G02DC-Q100 | Dual 2-input NOR gate | |

| 74HC3G04DC-Q100 | Triple inverter | |

| 74HC3G34DC-Q100 | Triple buffer gate | |

| 74HCT3G07DC-Q100 | Triple buffer with open-drain outputs | |

| 74AVCH2T45DC-Q100 | Dual-bit, dual-supply voltage level translator/transceiver; 3-state | |

| 74HC3G14DC-Q100 | Triple inverting Schmitt trigger | |

| 74HC2G08DC-Q100 | Dual 2-input AND gate | |

| 74AUP2G08DC-Q100 | Low-power dual 2-input AND gate | |

| 74LVC1G123DC-Q100 | Single retriggerable monostable multivibrator; Schmitt trigger inputs | |

| 74HCT2G08DC-Q100 | Dual 2-input AND gate | |

| 74HC3GU04DC-Q100 | Triple unbuffered inverter | |

| 74AHC2G08DC-Q100 | Dual 2-input AND gate | |

| 74AHC2G241DC-Q100 | Dual buffer/line driver; 3-state | |

| 74AHC2G125DC-Q100 | Dual buffer/line driver; 3-state | |

| 74AHC2G32DC-Q100 | Dual 2-input OR gate | |

| 74AHCT2G241DC-Q100 | Dual buffer/line driver; 3-state | |

| 74HC2G125DC-Q100 | Dual buffer/line driver; 3-state | |

| 74AHCT3G14DC-Q100 | Triple inverting Schmitt trigger | |

| 74AUP1G74DC-Q100 | Low-power D-type flip-flop with set and reset; positive-edge trigger | |

| 74AUP2G00DC-Q100 | Low-power dual 2-input NAND gate | |

| 74AUP2G80DC-Q100 | Low-power dual D-type flip-flop; positive-edge trigger | |

| 74HC2G00DC-Q100 | Dual 2-input NAND gate | |

| 74HCT2G32DC-Q100 | Dual 2-input OR gate | |

| 74AUP2G79DC-Q100 | Low-power dual D-type flip-flop; positive-edge trigger | |

| 74AVC2T45DC-Q100 | Dual-bit, dual-supply voltage level translator/transceiver; 3-state | |

| 74AUP2G125DC-Q100 | Low-power dual buffer/line driver; 3-state | |

| 74HCT3G04DC-Q100 | Triple inverter | |

| 74HC2G66DC-Q100 | Dual single-pole single-throw analog switch | |

| 74HC2G86DC-Q100 | Dual 2-input EXCLUSIVE-OR gate | |

| 74HC2G32DC-Q100 | Dual 2-input OR gate | |

| 74HC3G07DC-Q100 | Triple buffer with open-drain outputs | |

| 74HCT3G34DC-Q100 | Triple buffer gate | |

| 74HCT2G00DC-Q100 | Dual 2-input NAND gate | |

| 74HCT2G02DC-Q100 | Dual 2-input NOR gate | |

| 74LVC2G125DC-Q100 | Dual bus buffer/line driver; 3-state | |

| 74HCT3G14DC-Q100 | Triple inverting Schmitt trigger | |

| 74HCT2G86DC-Q100 | Dual 2-input EXCLUSIVE-OR gate | |

| 74LVC2G00DC-Q100 | Dual 2-input NAND gate | |

| 74LVC2G32DC-Q100 | Dual 2-input OR gate | |

| 74LVC3G17DC-Q100 | Triple non-inverting Schmitt trigger with 5 V tolerant input | |

| 74LVC3GU04DC-Q100 | Triple unbuffered inverter | |

| 74LVC1G53DC-Q100 | 2-channel analog multiplexer/demultiplexer | |

| 74HCT2G125DC-Q100 | Dual buffer/line driver; 3-state | |

| 74HCT2G66DC-Q100 | Dual single-pole single-throw analog switch | |

| 74LVC2G74DC-Q100 | Single D-type flip-flop with set and reset; positive edge trigger | |

| 74LVC3G34DC-Q100 | Triple buffer | |

| 74LVC2G08DC-Q100 | Dual 2-input AND gate | |

| 74LVC2T45DC-Q100 | Dual supply translating transceiver; 3-state | |

| 74LVC1G74DC-Q100 | Single D-type flip-flop with set and reset; positive edge trigger | |

| 74LVC2G66DC-Q100 | Bilateral switch | |

| 74LVC2G241DC-Q100 | Dual buffer/line driver; 3-state | |

| 74LVCH2T45DC-Q100 | Dual supply translating transceiver; 3-state | |

| 74LVC2G126DC-Q100 | Bus buffer/line driver; 3-state | |

| 74LVC2G02DC-Q100 | Dual 2-input NOR gate | |

| 74LVC2G240DC-Q100 | Dual inverting buffer/line driver; 3-state | |

| LSF0102DC-Q100 | 2-bit bidirectional multi-voltage level translator; open-drain; push-pull | |

| 74LVC2G86DC-Q100 | Dual 2-input EXCLUSIVE-OR gate | |

| 74LVC3G07DC-Q100 | Triple buffer with open-drain output | |

| 74LVC3G04DC-Q100 | Triple inverter | |

| NXS0102DC-Q100 | Dual supply translating transceiver; open drain; auto direction sensing | |

| NXU0102DC-Q100 | 2-bit dual-supply buffer/level translator with Schmitt-trigger; 3-state | |

| NXU0202DC-Q100 | 2-bit dual-supply buffer/level translator with Schmitt-trigger; 3-state | |

| NXB0102DC-Q100 | Dual supply translating transceiver; auto direction sensing; 3-state | |

| NCA9306DC-Q100 | 2-bit bidirectional multi-voltage level translator; open-drain; push-pull |